Redes neuronales

Implementación de redes neuronales en FPGA.

IAFE-UBA

Participantes:

Fernando Tanco (UTN-GIA)

Roberto Giacchetta (UTN-GIA)

Roberto Fernádez Borda (UBA-IAFE)

Las redes neuronales son implementadas en dispositivos de lógica programable (FPGAs) para su posterior aplicación en la detección de fulguraciones solares.

Marco Teórico:

Uno de los mayores inconvenientes para la implementación en hardware de redes neuronales es la cantidad de lógica necesaria para realizar la multiplicación de cada entrada por su correspondiente peso y las subsecuentes adiciones. El modelo matemático de una neurona puede expresarse de la siguiente manera:

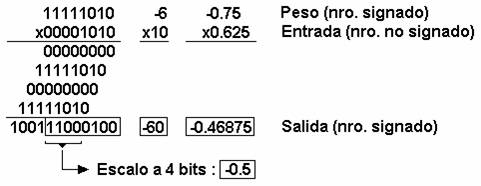

Donde xj son las señales de entrada, wji los pesos y ai la función de activación. Se optó por una arquitectura de multiplicación serie tipo “shift and add”. A continuación se muestra un ejemplo de un producto de dos números usando dicha arquitectura:

El multiplicando es un número de 4 bits signado (1010 binario = -6 entero = -0.75 decimal) y el multiplicador en un número de 4 bits no signado

(1010 binario = 10 entero = 0.625 decimal), como el producto va a resultar un número signado de 8 bits, se completa tanto el multiplicando como el multiplicador con el bit de signo para llevarlos a 8 bits. Se observa como los productos intermedios van siendo rotados una posición hacia la izquierda. Al final se realiza una suma de todos ellos y el resultado se obtiene de los 8 bits menos significativos. Si se quiere mantener el formato de 4 bits, escalo el resultado tomando los cuatro bits más significativos, aceptando el error que se comete: E% = (0.5-0.46875)/0.5 = 6.25% en este caso.

Requerimientos y Especificaciones:

Poder sintetizar en tres chips XC4010XL una red neuronal de arquitectura feed-forward de tres capas con 7 vectores de entada , 11 neuronas en la capa oculta y una neurona en la capa de salida.

Dicha red debe ajustarse a la red propuesta para la detección automática de fulguraciones solares. Diseño: El siguiente es un ejemplo de una unidad neurona con 8 entradas [Sal95], cada una acepta valores numéricos de 8 bits:

Cada unidad realiza la multiplicación de cada peso (8 bits signed) por su correspondiente entrada (8 bits unsigned) formando un producto de 16 bits signado. Los ocho productos son acumulados en un resultado de 20 bits (es la suma de productos). El resultado final se obtiene aplicándole una función de activación arbitraria a la salida del acumulador, este proceso escala el resultado intermedio a un valor de salida de 8 bits. El multiplexor selecciona cada una de las entradas de la neurona y la envía a un shift register de ocho bits con salida serie del bit menos significativo (shift right), el cual controla la habilitación del acumulador. Los pesos están almacenados en una look-up table de 8 bytes, uno para cada entrada y pasan a un shift register de 16 bits (salida paralela) que se encarga tanto de completar el byte más significativo con el bit de signo como de desplazar los valores hacia la izquierda. El acumulador se encarga de ir haciendo solo las sumas de los pesos desplazados según sea la señal de habilitación, la cual estará controlada por los ‘1’ provenientes del valor de entrada. Después de ocho ciclos se procesa la primer multiplicación, y después de 64 ciclos se procesa la sumatoria de los ocho productos. Luego se aplica a este resultado la función de activación almacenada en una look-up table de 256 bytes. Este último proceso escala el resultado intermedio de 20 bits a un valor de salida de 8 bits unsigned, el cual ya está listo para ser introducido a la entrada de otra neurona. El diseño incluye un sincronizador global para las señales de habilitación y reset de las neuronas. Se muestra un ejemplo de una red feed-forward con cuatro neuronas en la capa de entrada, cuatro en la capa oculta y dos en la capa de salida:

Implementación:

Software:

Xilinx Foundation Series 3.1i

Altera MAX+plus II 10.0

Matlab 6, Neural Network toolbox

Hardware:

Placa de desarrollo Xess XC4010XL (Xilinx)

Placa de desarrollo MAX7128 (Altera)

Observaciones:

El modelo de neurona se está sintetizando y simulando en un ambiente esquemático y luego se optimizará usando lenguaje VHDL. Las primeras pruebas arrojaron los siguientes resultados con respecto al “consumo” de lógica de una neurona:

Lógica base sin considerar las look-up tables: 51 CLBs.

Look-up tables de función activación y pesos: 15 CLBs (264 bytes).

Consumo total de una neurona: 66 CLBs.

Una FPGA tipo XC4010XL tiene 400 CLBs, por lo tanto por cada chip entrarían 6 neuronas aproximadamente

Paralelamente se está experimentando con otros dos modelos de neuronas basados en codificación de datos en bit streaming (flujo de datos serie) [Sal94] [GSM94] y en multiplicadores logarítmicos (mediante look-up tables) para tratar de disminuir el consumo de lógica de la unidad neurona.

Conclusiones:

Las neuronas podrán ser usadas para cualquier modelo de red, desde arquitecturas feed-forward hasta redes recursivas (Hopfield, Kohonen, etc). Capacidad de reprogramar la FPGA para generar el hardware correspondiente a cada modelo elegido. Debido a que el entrenamiento se realiza por software, no se requiere la implementación en hardware de dicha fase. La red neuronal será escalable, permitiendo la replicación masiva de neuronas, solo limitada por la capacidad lógica de la FPGA.

Bibliografía Recomendada:

- Implementación de redes neuronales en FPGA. Fernandez Borda

- Automatic flare detection using neural networks techniques. Gschwind, Salapura,Maischberger

Space efficient neural net implementation - Salapura. Neural networksusing bit stream arithmetic: a space efficient implementation

- Salapura. A fast FPGA implementation of a general purpose neuron